MIPS CPU Pipeline Simulation

Program takes 32bit instructions and models the flow through a cpu pipeline, manipulating simulated registers and memory.

This Python project simulates a data pipeline for a MIPS RISC architecture.

It includes functionalities for instruction decoding, execution, and memory access.

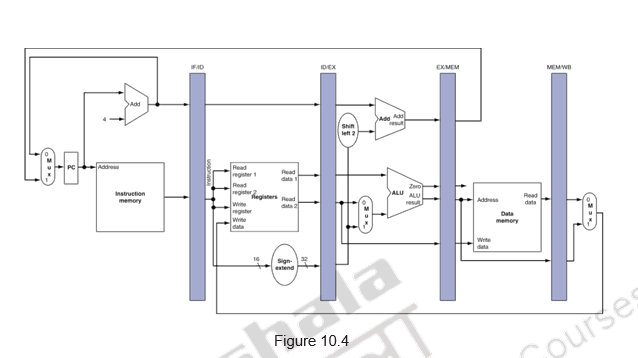

The code defines a set of control signals, instruction formats, and a data pipeline comprising several stages:

Instruction Fetch (IF), Instruction Decode (ID), Execute (EX), Memory Access (MEM), and Write Back (WB).

Each stage processes instructions sequentially. The project initializes memory, registers, and pipeline registers. It disassembles instructions, updating control signals based on the instruction type. The pipeline stages execute instructions, perform arithmetic and logic operations, and manage data transfers between registers and memory. The simulation iterates through the instruction cache, simulating clock cycles and updating pipeline registers at each stage. The execution continues until all instructions are processed. This project was completed as coursework in my Computer Architecture class.

Project URL: Github

Technologies Used: